## I/O 32<sup>TM</sup>

### User's Manual

## Applied Engineering

Telephone Numbers

### Technical Support

(214) 241-6069

9 AM to 12:30 PM & 1:35 to 5 PM (CST)

Monday through Friday

Do not return any product for service without a Return Material Authorization (RMA) number.

An RMA number can be obtained by calling Technical Support.

### Sales

(214) 241-6060

9 AM to 11 PM (CST) 7 days

## I/O 32<sup>TM</sup>

### User's Manual

#### Limited Warranty & Disclaimer

Applied Engineering warrants the I/O 32 card against defects in material and workmanship for a period of 5 years from the date of original retail purchase. Applied Engineering also warrants that, under normal use, the magnetic media on which the software is stored is free from defects in materials and workmanship for a period of 30 days from the date of original purchase. Any misuse, abuse, or non-Æ authorized alteration, modification and/or repair to the Applied Engineering product will void the warranty. This warranty will also be void if you use the Æ product for any other purpose than its intended use. If you discover a defect, Applied Engineering will, at its option, repair or replace only the Applied Engineering product, provided you return the product during the warranty period, transportation prepaid, to Applied Engineering.

This warranty applies to the original retail purchaser only. Therefore, please include a copy of the original invoice or a small service charge may be applied. If the product is to be sent to Applied Engineering by mail, the purchaser will insure the package or assume full responsibility for loss or damage during shipping. Prior to returning the product for warranty consideration, call Applied Engineering Technical Support for a Return Material Authorization (RMA) number and shipping instructions.

Even though Applied Engineering has tested the software and reviewed the documentation, Applied Engineering makes no warranty or representation, either express or implied, with respect to the manual or the software; their quality, performance, merchantability, or fitness for a particular purpose. As a result, the software and manual are sold "as is," and you, the purchaser, not Æ or its dealers, are assuming the entire risk as to their quality and performance.

In no event will Applied Engineering be liable for loss or damages of any kind caused either directly or indirectly by the use or possession of its products, even if advised of the possibility of such damages. The Applied Engineering Warranty is for the Applied Engineering Product itself. In particular, Applied Engineering shall have no liability for any other equipment used in conjunction with Applied Engineering products nor for programs or data stored in or used with Applied Engineering products, including the costs of recovering such equipment, programs, or data.

The warranty and remedies set forth above are exclusive and in lieu of all others, oral or written, express or implied. No Applied Engineering dealer, agent, or employee is authorized to make any modification, extension, or addition to this warranty.

Some states do not allow the exclusion or limitation of implied warranties or liability for incidental or consequential damages, so the above limitation or exclusion may not apply to you. This warranty gives you specific legal rights, and you may also have other rights which may vary from state to state.

This manual and the software (computer programs) described herein are copyrighted by Applied Engineering with all rights reserved. Under the copyright laws, this manual or the programs may not be copied, in whole or in part, without the written consent of Applied Engineering, except in the normal use of the software or to make an archival copy. This exception does not allow copies to be made for others, whether or not sold, but all of the materials purchased (with all archive copies) may be sold, loaned, or given to another person. Under the law, copying includes translating into another language or format. You may use this software on any computer owned by you but extra copies cannot be made for it is purpose.

Applied Engineering cannot guarantee that you will receive notice of revisions to the software, documentation or products described in this manual. Be sure to check with your dealer or Applied Engineering for information on possible updates. However, Applied Engineering reserves the right to make any improvements to Applied Engineering products without any responsibility toward upgrading previously released products.

Apple and Apple IIGS are registered trademarks of Apple Computer, Inc. Applied Engineering and I/O 32 are trademarks of Applied Engineering.

@Copyright 1988, Applied Engineering

Applied Engineering

P.O. Box 5100 Carrollton, Texas 75011

Sales: (214) 241-6060 9 AM - 11 PM (CST) 7 days

Technical Support: (214) 241-6069 9 AM - 12:30PM & 1:35PM - 5 PM (CST) Monday - Friday

(The Technical Support telephone lines cannot be accessed through the Sales department.)

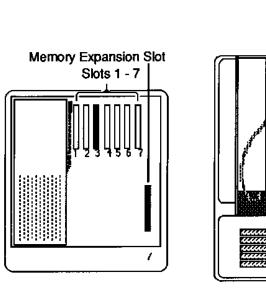

#### Installing the I/O 32 in Your Apple

The I/O 32 board simply plugs into a connector inside your Apple. Care must be exercised however, so follow these instructions exactly.

- 1) TURN OFF THE APPLE'S POWER SWITCH. This is very important to prevent damaging the computer as well as the I/O 32 board. However, you need to leave the computer plugged in throughout the installation to allow the power supply to discharge static electricity from your body.

- 2) Remove the cover from your Apple.

- --Pop the hood of the ][ Plus or //e by pulling up on the cover at the rear edge (the edge farthest from the keyboard) until the two corner fasteners pop apart.

- --The IIGS's lid has two fasteners on the sides of the back panel. Push in on the tops of the fasteners with your forefingers while pushing up with your thumbs and heel of your hands on the side of the lid.

- 3) Touch the power supply to remove any static electricity from your body. Do not skip this step! A static shock can damage the chips on your boards and/or the chips on your computer's motherboard.

- Locate the "slots" inside the Apple, across the rear of the main circuit board.

- 5) Plug the "fingers" of your I/O 32 board into any 1-7 expansion slot except slot 3. I/O 32 will not work in slot 0 of the ][+ nor the Auxiliary/Memory Expansion slot on the //e and IIGS. The "fingers" of the circuit board into the slot you want. The fingers will enter the slot with some friction and will seat firmly. (Refer to picture below.)

Inside the IIGS

Inside the )(, )(+ and //e

Auxiliary Slot (Ile only) Slot 0 (Il and II+ only)

Slots 1 - 7

- 6) Replace the Apple's cover by sliding the front edge into place, then press down on the two rear corners until they pop into place.

- 7) Now turn on your Apple and continue.

#### Features of the I/O 32

The I/O 32 has several features that make it very versatile. They allow you ease of use and changeability. The most important of the features is the onboard software (firmware). This software is contained in a 2716 EPROM (Erasable Programmable Read-Only Memory). This software allows you easy access to four ports. Within each port, you have eight pins which can be programmed as either input or output. Once you have set the desired direction, you can send or receive data in three formats. The formats are Decimal, Hexadecimal, and Binary. You can send data in any of the three formats and also receive in any of the three. The necessary commands to send or receive will be described in greater detail.

The I/O 32 also has four switches which allow you to configure the board for features other than the default values. The switch settings are described later.

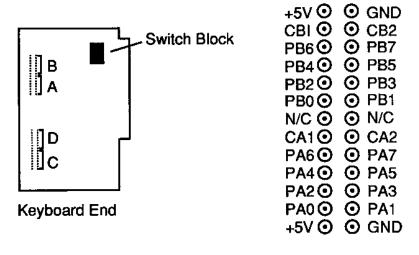

The I/O 32 uses two 6821 Peripheral Interface Adapter which give you the capability of using four 8-bit ports. Port A and Port C are TTL compatible and can drive tow TTL loads. Port B and Port D have high impedance inputs and push/pull outputs that can drive two TTL loads. (When used for a switch input, a 5K pull-up resistor is required.

\* PB = Port B, PA = Port A

The I/O 32 has 4 8-bit ports which can be programmed independently. The ports are labeled A, B, C, and D. Within each port there are 8 pins which are used for sending or receiving data. Each of the eight pins can be set as either input or output.

In order for you to use the I/O 32, you must build a cable that will suit your specific needs. The connector that you must acquire is available from several sources. Two are listed below:

Digi-Key

1-800-344-4539 Part No. R304-ND

**AP Products**

1-800-321-9668 Part No. 925110-26-R

These connectors will crimp onto standard 26 conductor ribbon cable.

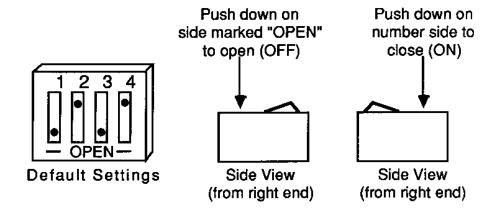

#### **Dip Switch Configurations**

On the I/O 32, there are four switches which allow you to configure your board for specific applications. The board was shipped to you with the switches in the default positions noted below in the diagram.

The switches can be used to enable different capabilities that are built into the I/O 32 board. As stated in the Features section of this manual, the I/O 32 has a 2716 EPROM containing the software necessary to make the card operate. This EPROM can store a program that is up to 2K-bytes in length. The software however, takes up only about half of the 2K so there is enough room left in the EPROM for a custom program to be permanently stored. If you had such a custom program in the same EPROM as the original software, you would simply move switch 4 to the open or off position. This will tell the Apple to look for a program in the upper half of the EPROM.

There is also another way to customize the I/O 32 without having to modify the EPROM. For instance, if the software on the board does not fit your needs, you could simply move switches 1 and 2 to their opposite state. This will disable the built-in software by telling the board and Apple that you are using a 6116 RAM (random access memory) chip instead of the 2716 EPROM. Once this is done, you could write your own software to control the input and output ports and have it loaded in from the disk every time you wanted to use it.

For those of you who need to have external devices linked with your I/O 32, you would set switch 3 to the on or closed position. This will enable the use of interrupts through program control. Interrupts using the I/O 32 will not be discussed in this manual.

#### Programming with the EPROM

Supplied with the I/O 32 board, is a program which will allow you easy access to the I/O ports. In order to use this software however, you must make sure that switch 1 is OPEN, switch 2 is CLOSED, and switch 4 is CLOSED. Once you have set the switches to the required position, you are ready to begin programming.

One of the easiest things to do at first is to locate the board through software. Since the card has software built in, we can search through the seven slots to look for particular parts of that program. To demonstrate this, type in this short program and then run it. When the program finishes running, it will return with a message telling you which slot the I/O 32 is located in. If it does not find it, it will tell you it did not find one.

```

1000 REM ***** Find the I/O 32 Board *****

1010 SLOT = 0

1020 FOR I = 1 TO 7

1030 ADDR = 12*4096+I*256: REM $Cs00 (where s is IO/32's slot number)

1040 IF PEEK (ADDR) = 44 AND PEEK (ADDR+1) = 88 AND PEEK (ADDR+254) = 201 THEN SLOT = I

1050 NEXT I

1060 IF SLOT = 0 THEN PRINT "No I/O 32 found!":END

1070 PRINT "I/O 32 found in slot ";SLOT

1080 END

```

After you have successfully located the slot of the I/O 32, you can proceed to programming the card itself. For the following examples, we will assume that your I/O 32 board is in slot 2.

When programming the I/O 32, you must follow certain steps in order to make sure that the data is correctly sent or received. To do this you must initialize the card. To accomplish this, all you need to do is call the card, then print the command. Type this program in and run it.

```

1000 REM ***** INITIALIZATION *****

1010 D$ = CHR$ (4)

1020 PRINT D$;"PR#2": PRINT D$;"IN#2"

1030 PRINT "I"

1040 PRINT D$;"PR#0": PRINT D$;"IN#0"

1050 END

```

Lines 1010 and 1030 selects and deselects the I/O 32. Line 1020 sends the necessary information to initialize the I/O ports. Sending this command has two effects:

- 1) Set all four ports to input only.

- 2) Disable all interrupts.

The next step in programming the I/O 32 ports is to set the desired direction for data. Type this program and run it.

```

1000 REM **** SET DATA DIRECTION *****

1010 D$ = CHR$ (4)

1020 PRINT D$;"PR#2": PRINT D$;"IN#2"

1030 PRINT "A($FF)"

1040 PRINT D$;'PR#0": PRINT D$;"IN#0"

1050 END

```

As with the initialization command, lines 1010 and 1030 select and deselect the board. Line 1020 is the command that sets the direction for data. The "A" is the port letter. You could have specified any one of the four, but we will use port A. The number is given here in hexadecimal (\$FF) but to the I/O 32 it is "11111111" in binary. Notice there are 8 1's. Also notice under the section on the User Connection that in each port there are 8 pins for sending or receiving data. Each 1 corresponds to one pin on the port selected, and a "1" means output, so the above program sets port A to all output. Once both of the above steps have been completed, you are ready to send data.

Let's for a minute, assume that you had 8 light bulbs that you wanted to turn on or off. You could hook up each of the eight lights to each of the 8 pins on port A (see the section "User Connection"). Then to turn a light on, you would just send the appropriate code to do so. For example:

```

1000 REM ***** TURN ON PIN 4 *****

1010 D$ = CHR$ (4)

1020 PRINT D$;"PR#2": PRINT D$;"IN#2"

1030 PRINT "I": PRINT "A($FF)"

1040 PRINT "A$10"

1050 PRINT D$;"PR#0": PRINT D$;"IN#0"

1060 END

```

Line 1020 should be familiar to you. This line combines the initialization command and the direction command. Line 1040 is the data to be sent to port A to turn our light on. The "\$10" is again given in hexadecimal but the I/O 32 sees it as "00010000". In this example, the 1 does not mean output as it did in setting the direction, it means on. This command just sends data to turn on or off a selected number of pins. If you wanted to turn light 4 off and lights 7 and 8 on, you would change line 1040 to: 1040 PRINT "A\$03"

This command sends the binary code "00000011" to port A and turns off light 4 and then turns on lights 7 and 8.

The above programs are used to turn on and off lights when you already know their present state. However, through program control, you could check to see which ones are on and which ones are off. You would do this with the input command. At this time, we should still have lights 7 and 8 on.

Make sure 7 and 8 are still on with this program.

```

1000 REM ***** CHECK STATE *****

1010 D$ = CHR$ (4)

1020 PRINT D$;"PR#2": PRINT D$;"IN#2"

1030 INPUT "A%";X$

1040 PRINT D$;"PR#0": PRINT D$;"IN#0"

1050 PRINT X$

1060 END

```

Lines 1010 and 1020 are the same as for output. The change comes in line 1030. When inputting data, we use the DOS input statement, then the port letter and value mode followed by the variable to store the data into. In line 1050, we print the data that was input in line 1030.

After you have typed this program and executed it, you will have accomplished all the basic commands that are dealt with by the I/O 32. Further programs can be derived from the following table of syntax commands.

#### **Output Syntax**

```

PRINT "<port><data.value>" PRINT "A#15"

PRINT "<port><ddr.value>" PRINT "A($FF)"

PRINT "<port><ddr.value><data.value>" PRINT "A($FF)#15"

```

NOTE: The <ddr.value> is the value that determines which of the 8 pins in each port are input or output.

#### **Input Syntax**

NOTE: The <ddr.value> is the value that determines which of the 8 pins in each port are input or output.

When <port> and/or <value.mode> are missing with the INPUT command, the previously specified port and mode will be used. If you have not previously specified both of those, you will get unpredictable results.

#### **Acceptable Values**

With the built-in software, there are values that must be used in order to prevent errors when running a program. The values are:

<port> A

B

C

<value.mode> \$ - hexadecimal

# - decimal

% - binary B - binary

<digits> hexadecimal 0-9 and A-F

decimal 0-9 binary 0 and 1

The port value and digits are self explanatory however, the value mode needs a little explaining. Whenever you want to send or receive data you must specify one of the three modes. Once you specify which mode you wish to use, you simply send the appropriate value. For example if you wanted to send a value of 26 decimal, you could also send it as IA hexadecimal or 00011010 in binary, just by specifying the mode and then the value you wish to send.

#### **Maximum Values**

With each of the acceptable values above, there are certain limitations on the maximum number that can be entered into the I/O 32. The maximum values are for <digits> only.

HEXADECIMAL 0-FF

DECIMAL 0 - 255

BINARY 00000000 - 11111111

DO NOT EXCEED THESE VALUES OR YOUR PROGRAM WILL HALT SUDDENLY!

#### **Sample Programs**

Below is a sample program that will give you some idea of how to use the I/O 32 under software control.

#### Sample Program

```

1000 REM ***** DEMONSTRATION *****

1010 GOSUB 10000: REM FIND I/O 32

1020 PRINT CHR$ (4); "PR#"; SLOT

1030 PRINT "I": PRINT "A($FF)"

1040 PRINT CHR$ (4); "PR#0"

1050 TEXT:HOME

1060 INPUT "ENTER VALUE TO SEND: "; V$: IF V$=" " THEN END

1070 PRINT CHR$(4); "PR#"; SLOT: PRINT CHR$(4); "IN#"; SLOT

1080 PRINT "A$"; V$

1090 INPUT "A$";D1$

1100 INPUT "A#";D2$

1110 INPUT "A%";D3$

1120 PRINT CHR$(4);"PR#0": PRINT CHR$(4);"IN#0"

1130 PRINT "PORT A - HEXADECIMAL ";D1$

1140 PRINT " - DECIMAL ";D2$

1150 PRINT " - BINARY

";D3$

VTAB 6:PRINT "PRESS ANY KEY TO CONTINUE...": GET A$

1160

1170

GOTO 1050

1180 END

10000 REM ***** FIND I/O 32 BOARD ***** 10010 SLOT = 0

10020 FOR I = 1 TO 7

10030 ADDR = 12*4096 + I*256: REM $CS00

IF PEEK (ADDR) = 44 AND PEEK (ADDR+1) = 88 AND

10040

PEEK (ADDR+254) = 201 THEN SLOT = I: I = 7

10050 NEXT I

10060 IF SLOT= 0 PRINT "NO I/O 32 FOUND!": END 10070 RETURN

```

#### Peripheral Driver Chips for the I/O 32

Following are the part numbers for 500mA (max.) inverting driver chips that can be used to drive DC lamps, relays etc. with the I/O 32. This is just a partial list. Manufacturer data sheets and catalogs may be able to point you to other drivers.

```

Chips with 8 drivers

```

ULN2803 Motorola ULN2803 Sprague

Chips with 7 drivers

MC1413 Motorola ULN2003A Sprague

Check the manufacturer's data sheets for pin-out information, etc.

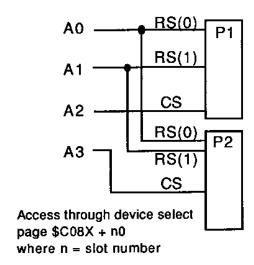

#### **IO/32 Address Bits**

Machine Language Programmers: the following address register charts are provided to help you address the chips directly.

If you're not interested in machine language programming, ignore this section.

#### The 6502 Address Registers in Slot s

|                                     | CRA          | CRB                  |                                       |                                        |

|-------------------------------------|--------------|----------------------|---------------------------------------|----------------------------------------|

| <u>Address</u>                      | <u>Bit 2</u> | <u>Bit 2</u>         | <u>Read</u>                           | <u>Write</u>                           |

| \$C084+s0                           | 1            | -                    | Port A In                             | Port A Out                             |

| \$C084+s0                           | 0            | -                    | Data Dir A                            | Data Dir A                             |

| \$C085+s0                           | -            | -                    | Ctrl Reg A                            | Ctrl Reg A                             |

| \$C086+s0                           | _            | 1                    | Port B In                             | Port B Out                             |

| \$C086+s0                           | -            | 0                    | Data Dir B                            | Data Dir B                             |

| \$C087+s0                           | -            | -                    | Ctrl Reg B                            | Ctrl Reg B                             |

|                                     |              |                      |                                       |                                        |

|                                     |              | _                    | • • • •                               |                                        |

|                                     | CRA          | CRB                  |                                       |                                        |

| Adress                              | CRA<br>Bit 2 | CRB<br>Bit 2         | Read                                  | <u>Write</u>                           |

| <u>Adress</u><br>\$C088+s0          |              |                      | Port C In                             | Port C Out                             |

|                                     | <u>Bit 2</u> |                      | Port C In<br>Data Dir C               | Port C Out<br>Data Dir C               |

| \$C088+s0                           | Bit 2<br>1   |                      | Port C In                             | Port C Out                             |

| \$C088+s0<br>\$C088+s0<br>\$C089+s0 | Bit 2<br>1   |                      | Port C In<br>Data Dir C               | Port C Out<br>Data Dir C               |

| \$C088+s0<br>\$C088+s0              | Bit 2<br>1   | Bit 2<br>-<br>-<br>- | Port C In<br>Data Dir C<br>Ctrl Reg C | Port C Out<br>Data Dir C<br>Ctrl Reg C |

```

Bit 7 IRQx1 Flag

IRQ caused by Cx1 transition (cleared by reading Port x)

1

0

No IRQ

When Bit 5 = 0

Bit 6 IRQ Flag

IRQ caused by Cx2 (cleared by reading Port x)

1

0

No IRQ

Bit 5 Cx2 Mode Select

0 .

Select cx2 Input Mode

Bit 4 Cx2 polarity for IRQ

Set IRQx2 (bit 6) for low-to-high transition of Cx2

1

0

Set IRQx2 (bit 6) for high-to-low transition of Cx2

Bit 3 IRQx enable for IRQx2

1

Enable IRQx

0

Disable IRQx

When Bit 5 = 1

Bit 6 Always 0

Bit 5 Cx2 Mode Select

1

Select cx2 Output Mode

Bit 4 Cx2 Output Control

Cx2 goes low when a 0 is written to CRx bit 3

1

Cx2 goes high when a 1 is written to cRx bit 3

0

Cx2 goes low in the first high-to-low transition of phase 0

after a read of Port x

Cx2 goes high as specified by bit 3

Bit 3 Cx2 read strobe restore control (bit 4 = 0)

Cx2 goes high on the next phase 0 clock high-to-low

transition following a read of Port x

0

Cx2 goes high on the next active Cx1 transition as specified

by bit 1

Bit 2

Port x I/O or Data Direction Select

1

Port x

Data Direction Register for Port x

0

Cx1 polarity for IRQ

Bit 1

Set IRQx1 (bit 7) for low-to-high transition of Cx1

1

Set IRQx1 (bit 7) for high-to-low transition of Cx1

0

Bit 0 IRQx enable for IRQx1

1

ENable IRQx

Disable IRQx

0

```

If a bit in the Data Direction Register is 1, the corresponding bit of the Port is an output; otherwise, it is an input.

The procedure for writing to an output is:

- 1) Write a 0 to bit 2 of the Control register.

- 2) Write 1's to the Data Direction Register of each output bit.

- 3) Write a 1 to bit 2 of the Control Register.

- 4) Write data to the Port.

The procedure for reading from an input is:

- 1) Write a 0 to bit 2 of the Control Register.

- 2) Write 0's to the Data Direction Register of each input bit.

- 3) Write a 1 to bit 2 of the Control Register.

- 4) Read data from the Port.

Control Reg A \$C085+s0 Control Reg B \$C087+s0 Control Reg C \$C089+s0 Control Reg D \$c08B+s0

Examples are included on the following page.

#### Examples:

| Reading all 8 bits from Port A<br>LDA \$C085+s0<br>AND #%11111011<br>STA \$C085+s0<br>LDX #\$00<br>STX \$C084+s0<br>ORA #%00000100<br>STA \$C085+s0<br>LDA \$C084+s0       | ;Read Control Register A ;Turn off bit 2 ;Set CRA for Data Direction ;All bits are inputs ;Set Data Direction for all inputs ;Turn on bit 2 ;Set CRA for Port A data ;Read Port A data                               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Writing all 8 bits to Port D LDA \$C08B+s0 AND #%11111011 STA \$C08B+s0 LDX #\$FF STX \$C08A+s0 ORA #%00000100 STA \$C08B+s0 LDA #\$AE STA \$C08A+s0                       | ;Read Control Register D ;Turn off bit 2 ;Set CRD for Data Direction ;All bits are outputs ;Set Data Direction for all outputs ;Turn on bit 2 ;Set CRD for Port D data ;Data to write ;Write Port D data             |

| Reading bit 0, 1, 2 from Port B<br>LDA \$C087+s0<br>AND #%11111011<br>STA \$C087+s0<br>LDX #%11111000<br>STX \$C086+s0<br>ORA #%00000100<br>STA \$C087+s0<br>LDA \$C086+s0 | ;Read Control Register B<br>;Turn off bit 2<br>;Set CRB for Data Direction<br>;Bits 0,1,2 are inputs<br>;Set Data Direction<br>;Turn on bit 2<br>;Set CRB for Port B data<br>;Read Port B data                       |

| Writing bits 4, 5, 6, 7 to Port C LDA \$C089+s0 AND #%11111011 STA \$C089+s0 LDX #%11110000 STX \$C088+s0 ORA #%00000100 STA \$C089+s0 LDA #\$A0 STA \$C088+s0             | ;Read Control Register C<br>;Turn off bit 2<br>;Set CRC for Data Direction<br>;Bits 4,5,6,7 are outputs<br>;Set Data Direction<br>;Turn on bit 2<br>;Set CRC for Port C data<br>;Data to write<br>;Write Port C data |

#### 6821 Data Sheets

The following pages include the technical information about the Hitachi HD6821 chip found on the I/O 32 board. The selected pages have been reprinted from, <u>8/16-Bit Multi-Chip Micro Computer Data Book</u>, <u>U70</u>, pages 319-335 with permission from:

Hitachi America, Ltd. Semiconductor & I.C. Sales and Service Division

## HD6821, HD68A21, HD68B2 (Peripheral Interface Adapter) PIA

The HD6821 Pertpheral Interface Adapter provides the unvestal means of interfacing pertpheral equipment to the HD6800 Misroponessing Unit (APU). This devoke is espained interfacing the MPO to perspherals through two 8-bit bedirectional peripheral data buses and four control lines. No exercial logic is required for interfacing to most peripheral

The functional configuration of the PIA is programmed by the MEU demy system inflatabilisation. Each of the peripheral data lines can be programmed to said as an input or output, and each of the four control/interapt lives may be programmed for one of several control modes. This allows a high degree of flexibility in the overall operation of the interface.

E PIN ARRANGEMENT

- FEATURES

- Two Bi-directional B-Bit Peripheral Data Bus for interface Peripheral devices

- Two Programmable Control Registers Two Programmable Data Direction Registers Four Individually-Controlled Interrupt Input Lines: Two

- Useble as Peripheral Control Outputs

Handshale Control Logic for Input and Output Pari

- and Direct Transistor Drive High-Impedence 3-State pheral Operation

- Program Controlled Interrupt and Interrupt Disable

- CMOS Drive Capability on Side A Peripheral Lines Two TTL Drive Capability on All A and 8 Side Buffers

- N Channel Silicon Gate MOS

Compatible with MC5821, MC58A21 and MC58B21

- BLOCK DIAGRAM

HD6821 o

(Top View)

# - PIA INTERFACE SIGNALS FOR MPU

The PLA interfaces to the HD6800 MPU with an eight-bit bedirectional data bus, three dups afect lines, two rapisers afect of new two interpers request lines, racklywrite line, stable lines after line. There agains, in comparation with the HD6800 VMs, conjust, permit the MPU to have complete control over the PLA. VMs should be utilized in conjunction with an MPU address line into a represent to the PlA, what should be utilized in conjunction with an MPU address line into a represent of the Da. Da. I allow the transfer of the bidiencetonal data lines (Do. Do.) allow the transfer of the bidiencetonal data lines (Do. Do.) allow the transfer of the bidiencetonal data lines (Do. Do.) allow the transfer of the bidiencetonal data lines (Do. Do.) allow the transfer of the bidiencetonal data lines are expert when the MPU performs a PIA read operation. The list line if in the PIA is selected for a Read operation.

Ar min in the read, then just what in the read operation.

\*\* PA Exable IE;

\*\* The enable IE;

\*\* The enable IE;

\*\* The enable in the conjustion of the state o

These three input signals are used to elect the PIA. CSo and CS<sub>2</sub> must be "High" and CS<sub>2</sub> must be "Low" for selection of the electic. Dust namides at a tun performed under the control of the E and RIV usuals. The chip select times must be stable for the duration of the E puts. The chew is deselected when • PIA Chip Select (CS<sub>0</sub>, CS<sub>1</sub> and CS<sub>1</sub>)

any of the chip schecus are ut the inactive state.

• PA Registers Scheet (RS<sub>2</sub> and CS<sub>2</sub>).

The two register select lines are used to select the various register stade that are used as conjunction registers stade the Pla. These two lines are used as conjunction with internal Control Registers to select a particular register that

with infinit (windon Keggers) to where a printional register that is to be written our read.

The register and chip select lines should be stuble for the duration of the k-pairs while in the read or writt eyeld.

I the series "Low" laterage Kequets lines (ROA and ROB) at to interrupt the MPU selfer directly. Then lines are "Open distail" load devece on the chip. This permits all interrupt request lines (ROA and ROB) and to the chip. This permits all interrupt request lines load devece on the chip. This permits all interrupt request lines and devece on the chip. This permits all interrupt request lines to be tred together in a wire-ON configuration.

Each ROB line has two interrupt interrupt flag bits that can cause the ROB line to go "Low" is faced flag bit is associated with a particular persphered in the PIA within may be used to initiality a surface interrupt from a perplicate device.

Survicing an unterrupt by the MPU may be exemplished by a software counter that, on a providized basis, sequentially reads and sess the two control registers in each PIA for interrupt flag bits that are set.

The interrupt flags are cleared (seroed) as a result of an MFC. Read Principal in Data Operation of the companyoding drawgement. After being clared, the interrupt flag bit cannot be embled to be set until fine Pfu & descioused during all galax. The E paths is used to condition the interrupt control lines (CA<sub>2</sub>, CA<sub>2</sub>, CB<sub>3</sub>, CB<sub>3</sub>). When these lines are used as interrupt inputs at least one E pulse must occur from the interrupt control lines (edge across returned to the interrupt of the interrupt of the series edge to the interrupt flag has been establed and the edge series edge to the interrupt flag has been establed and the edge series edge to the heavy of the series of the party conditioned, the interrupt flag will be act on the next active transition of the interrupt flag but the transition of the

# . PLA PERIPHERAL INTERFACE LINES

The PIA proodes we debut be directional data bases and Coursingerup/Control large for infertication to perioheral devices.

• Section A Proopers Date (Pa<sub>0</sub>—Pa<sub>1</sub>) and the control of the peripheral data large and be programmed to act as an input. Date in the statement of the terribural data large but for those lines which are to be coupting. A "V" in a bit of the Date Direction Register causes the corresponding peripheral data line to act as an input. Daries as May URead Pripheral Data Operation, the data on peripheral lines programmed to act as input appears directly on the corresponding peripheral Data A" openition, the register causes the corresponding peripheral Data A" openition while a "O" results an a" "Low". Data in Culptur Register A will appear on the data lines that are programmed to be output. A logical "I" written min the register will cause a" High?" on the corresponding lines are programmed as a "High." On the Corresponding lines are programmed as output. This data will be early properly fire vollage on the peripheral data lines in greater than 70 volts for a logic "I" output and the state of the data of the control of the place on the propheral data lines in greater than 70 volts for a logic "I" output and less than 0.

The proper medium of the MeY, on a Read operation to differ from the continued to an as either firming or neutput lines much the evalue acquelities, allowing them to mare a high impedance state when the properly from hose lines programmed as output is the end of the properly from hose lines programmed as output is the end of the black in the properly from book lines programmed as output when the properly from hose lines programmed as output when the properly from book lines programmed as output when the properly from book lines programmed as output even if the vollage are applicitly, allowing them in used as a reput in datalition, data on the peripheral data lines Pa<sub>1</sub>-Pa<sub>2</sub>. They have these some puber of the proop of the proper properly from the peripheral data lines Pa<sub>2</sub>-Pa<sub>2</sub>

interpretable to a transfero switch,

- interpretable theor (CA, and CB, 1

Perspheral Input Lines (CA, and CB, are imput only lines that

Perspheral Input Lines (CA, and CB, are imput only lines that

the interpretable flags of the control registers. The active

transition for these against as also programmed by the two

Periphial Control (CA, )

Periphial Control (CA, )

The propher Lournil like CA, can be programmed to act as an interrupt input or at a peripheral control output. As an output, this little accordance in the standard Carlo (CA, )

Peripheral Control (CB, )

Peripheral Control (CB, )

Sa in interrupt input or peripheral control like (SB, may also be programmed to act as an interrupt myst or peripheral control line (SB, may also be programmed to act as an interrupt myst or peripheral control line (SB, may also be programmed to act as an interrupt myst or peripheral control output, As an input.

**GHITACE**

318

**BHITACH**

HD6821,HD68A21,HD66B21

+D8821, HD88A21, HD88B21

this has has "High" input impedance and is compatible with readed TT. As a couper tile scompatible with standard TT. As an output it is compatible with standard TT. As and may also be used as a source of up to 2.5 millimpere (typ) in 1.5 woit to discussing drive the base of a terminator switch. This there is so you served to the total Register B.

NOTE I. Listerney' knysus CA., CA., CB. and CB. had be used at normal "High" beat, When interrupt input are "Low" it nest (RES = "Low"), whereany fugure CA. CA., CB. and CAB. Than B.

2. Pulse width of interrupt inputs CA., CA., CB, and CB. paid be greater than a E eyel eithe. In the case that "High" then of B agand is not excitated in laternays pulse, an unterrupt flags may not be set.

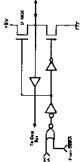

The equivalent Circuit of the Lines on Peripheral side.

The equivalent circuit of the lines on Peripheral side is rhown.

In Eg. 35. The output circuits of A port is different from that of B port. When the port is used as input, the input is beginning to A port and as input, the input is beginning to Arg. side through look MOS in A port and B port become "Off" (MgH impedince).

(a) Section A

(b) Section 8 Figure 15 Peripheral Data Bus

\* INTERNAL CONTROLS

There are in Louison within the PLA accessible to the MPU

data bus; two Penpineral Registers, two Data Direction Redistrict, and two Control Registers. Selection of these locations in

controlled by the RS, and RS, input to igniter with bit 2 in the

Control Register, as shown in Table 1.

CREO are used to enable the MeVI bearuph algoria INGA and INGO, supercisely. But CAAL and CREO, determine the active transition of the hostrapi sport algoria CA<sub>3</sub>, and CB<sub>3</sub>. (Table 3) Control of CA<sub>3</sub>, and CB<sub>3</sub>. (Table 3) Control of CA<sub>3</sub>, and CB<sub>3</sub>. (Table 3) CAAAA, CHEO, CHEO, CHEO, and CB<sub>3</sub>. (Table 3) CHEO, SIGH, and CB<sub>4</sub>. (Table 4) When CRAS (CREO) is "In the transport input line similar in CAA (CREO) is """. (Table 4) When CRAS (CREO) is """. (Table 4) When CRAS (CREO) is """. (Table 4) When in the catiput mode, CA<sub>3</sub> and CB<sub>3</sub>. have allightly different characteristic (Table 5 and 6).

Date Derestiens Access Control paint (CRAZ and CABEZ)

Bit 2 in such Control pagistre (CRA and CRB) allows relection of either a Peripheral Interfee Register or the Date Development of the CRB allows the Development of the CRB allows the Development of the CRB (CRAZ, CRAZ, CRAZ, CRAZ, and CRES).

Interpret Flugs (CRAZ, CRAZ, CRAZ, CRAZ, and CRES) also the CRAZ (CRAZ, CRAZ, and CRES).

The four bistropy flug bits are as the pacifier resultions of signed out the four interrupt and Peripheral Control lines when those lines are programmed to be suggested. The control lines when the Brad fourtheral Date Operation on the appropriate section.

Control of CA, and CB, inservant Lines (CRAG, CRAZ), CRAZ, and CRAZ, and CB, inservant Lines (CRAG, CRAZ), CRAZ,

|   |                                       | Location Selected | Perspheral Regulater A.* | Data Direction Regimer A | Control Reproter A | Paripharet Ruginter B" | Branden Arecton Branders B | Control Register B |

|---|---------------------------------------|-------------------|--------------------------|--------------------------|--------------------|------------------------|----------------------------|--------------------|

|   | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | CHB3              | ×                        | ĸ                        |                    | -                      | •                          | ×                  |

| İ | Control<br>Register S                 | CHAZ              | 1                        | •                        |                    |                        |                            | •                  |

|   |                                       | £                 | 0                        |                          |                    | ۰                      | ٥                          |                    |

|   |                                       | ž                 | a                        | ٥                        | ٥                  | -                      | -                          | -                  |

x = Don't Citie

\* Perspherel interface reputer as poperanc form containing perspherel

date bus and output register,

A "Low" reset line has the effect of zeroing all PIA registers. This will set PA—APA, "B—B—B, "CA, and CB, as inputs, and all interrupts distable. The PIA must be configured during the mast program which follows the reset.

Details of possible configurations of the Data Direction and Control Register are as follows.

Data Discretion Registers (IDDRA and DDRB)

The two Data Discretion Registers allow the MPI to control

the direction of date shough each corresponding peripheral

data line. A Data Direction Registers bit set at "0" configures the

outsponding peripheral data line as an input: a "1" results in

an output.

Control Pugiture (CRA and CRB) allow the MPU to

The two Control Registers (CRA, and CRB) allow the MPU to

Charlos the operation of the four peripheral control lines CA<sub>1</sub>.

CA<sub>2</sub>, CR, and CR<sub>2</sub>, in addition they allow the MPU to enable

the interrupt lines and nomitor the status of the interrupt lines.

Bits 0 through 5 of the two registers may be written on read by

the MPU when the proper they where and one read on the status of the cut and

the applied. Bits 6 and 2 of the two registers are read only and

are applied. Bits 6 and 3 of the two registers are read only and

are modified by external interrupts occurring on control lines

(CA<sub>1</sub>, CA<sub>2</sub>, CB<sub>3</sub> or CB<sub>3</sub>.) The format of the control words is

shown in Table 2.

|            |           | a pie | 8  | 0           | Mord | able 2 Control Word Format |       |             |

|------------|-----------|-------|----|-------------|------|----------------------------|-------|-------------|

|            | 7         | 9     | •  | *           | F    | 2                          | ı     | 0           |

| 4          | CRA (ROA) | IRGA2 | ធំ | CA, Control | 10   | DORA                       | 5     | CA, Control |

|            | ,         | æ     | 5  | 4           | ~    | 2                          | -     | ۰           |

| CAB<br>CAB | 19Dei     | 28041 | Ü  | B: Comrol   | 5    | ##CO                       | 0 180 | CB, Control |

ž

325

Table 3 Control of Interrupt Inputs CA, and CB

The two lowest order bits of the control ragisters are used to constrol the interrupt input lines  $CA_1$  and  $CB_1$  . Bits CRA0 and

| MPU Interrupt<br>Request<br>(RGA (IRGB) | Diabled – IRO remains<br>"High" | Goes "Low" when the inter-<br>rupt fleg bit CRA7 (CR87)<br>goes "1" | Diesbied - ING remeins<br>"High" | Goes "Low" when the inter-<br>rupt fleg bit CRA7 (CRB7)<br>goes "1" |

|-----------------------------------------|---------------------------------|---------------------------------------------------------------------|----------------------------------|---------------------------------------------------------------------|

| Interrupt Fiag<br>CRA7 (CRB7)           | Set "\$" on ↓ of CA,<br>(CB,)   | Set "I" on 4 of CA <sub>1</sub><br>(CB <sub>1</sub> )               | Set "1" on 1 of CA;<br>(CB;)     | Set"1" on 1 of CA,<br>(CB,)                                         |

| Interrupt Input<br>CA, (CB,)            | 4 Active                        | 4 Active                                                            | 1 Activa                         | 1 Active                                                            |

| CRA0<br>(CRB0)                          | ۰                               | -                                                                   | ٥                                | _                                                                   |

| CARB)                                   | 0                               | •                                                                   | -                                | -                                                                   |

ister.

Control of CA<sub>2</sub> and CB<sub>2</sub> as Interrupt Inputs — CRAS (CRBS) is "O"

| MPU Interrupt<br>Request<br>IRGE (IRGB) | Disabled – IMO remains<br>"Hight"                     | Goes "Low" when the inter-<br>rupt flag bit CRA6 (CRB6)<br>goes "";" | Disabled - IRQ remains                                | Goes "Low" when the inter-<br>rupt fleg bit CRA6 (CR86)<br>goes "1" |  |

|-----------------------------------------|-------------------------------------------------------|----------------------------------------------------------------------|-------------------------------------------------------|---------------------------------------------------------------------|--|

| (nterrupt Flag<br>CRA6 (CR86)           | Set "1" on ↓ of CA <sub>1</sub><br>(CB <sub>1</sub> ) | Set "!" on ↓ of CA <sub>2</sub><br>(CB <sub>2</sub> )                | Set "1" on t of CA <sub>2</sub><br>(CB <sub>2</sub> ) | Set "1" on f of CA <sub>2</sub><br>(CB <sub>2</sub> )               |  |

| (mercupt input<br>CA; (CB;)             | J Active                                              | J. Active                                                            | 1 Active                                              | † Active                                                            |  |

| CRR3)                                   | 0                                                     | -                                                                    |                                                       | ı                                                                   |  |

| CRA4<br>(CRB4)                          | 5                                                     | 0                                                                    | -                                                     | -                                                                   |  |

| CRAS                                    | 0                                                     |                                                                      | ٥                                                     | ٥                                                                   |  |

Interrupt Tag bis 1974 is delened by an MPU Panal of the A Perspheral Reporter and CR06 of set by the MPU Reset of Perspheral Reports.

Set by an MPU Reset of Perspheral Reports.

Set 2, (1982) is "Offer when an interrupt occurs (Interrupt disabled) and is less brought.

IRGA (IRGB) occurs also CR42 (CR03) is wenten to a "1".

##04 ) • Set DORB access bit of the control register to "1" to allow to CRB access the peripheral interface register. The date of which Date control line function is set into the accountability, of which Date Direction Register Access Bit shall be programmed to 'T'.

Thractic the control date from the accountaintoe into the count of pajeter. CPA . Chear the DDRA access bit of the control register to "U".

DDRA . C Chea Bit in of the dead discussion register.

SEI DDRA access bit of the control register to "!" to allow cna.

To access the portphent interface register. Program the data direction register second bit of the control register to "G" to allow to societ the dada direction register. CRA • Set DDRB access bit of the control register to "O". \*#FF } • Set all bits of the data direction register to "FF". DATA) • Write the data into the peripheral interface register. **BHITACH** Ĭ institution

When the external reset kepet RES goes "Low", all internal registers are delived to "O". Published point "D", Published to per (Re-PAT)

PL, "PE, ) is defined to be input and control lims (CA, ; CA, ; CB, and CB, ) are defined to be the interrupt input limes. PL is see infinitioned by software sequence as follows. STAA - AAT . 1949 5 5 5 5 E Rand/Write Operation Not Using Control Lines < Read Operation> DOM oral metahweed on emb terrinos eta beau Brone the contents of ACC into the control register Store the days in the accumulator into output register Load the contents of the peripheral interface register into the somewheletor Set the date direction reguter to HFF. Set the data direction register to "OO" Store the upwenty of ACC into the chee direction regime Initialize the control regator HO8821, HD68A21, HD68B21 (Sear The control register Infinition the Offithe Operation> - MA OPERATION 328 Set CRR7 is set by when the interrupt flag bit CRR7 is set by an active transition of the CRR yields and the flag bit CRR7 in the flag bit of the flag in the flag 327 "High" when the intercupt flag bit CRA7 is set by an explore transition of the CA, signel. (See Figure 16) "High" on the negative edge of the first "E" pulse which occurs during a classifict. (See Figure 16) HD6821,HD88A21,HD68B21 "High" (The content of CRA3 is output on CA<sub>2</sub>) "Low" (The content of CRA3 is output on CA<sub>2</sub>) "High" (The content of CRB3 is output on CB<sub>3</sub>) "Low" (The content of CR93 is output on CB<sub>3</sub>) Table 6 Control of CA<sub>2</sub> as an Output — CRAS is "1" Table 5 Control of CB; M an Output - CR65 is "1" "Low" on the positive transition of the first E pulse if the MPU. Write "B" Data Register operation. "Low" on the positive transition of "Low" in the positive transition of the first E pulse after an MPU Write "B" Data Register operation. "Low" on negative transition of E after an MPU Read "A" Data Opera-tion. "Low" on negative transition of E after an MPU Raid "A" Data opera-tion. **⊕** HITACHI CRB3 CHA3 ۰

SR C

CHAS

CA 84

CR85

Read/Write Operatory Using Control Lines

Read/Write request from propherals shall be put into the control lines as an interrupt signal, and then MPU reads or writes after detecting interrupt's equal.

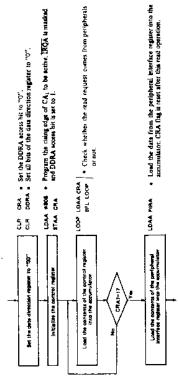

The following case is that fort A is used and that the rising edge of CA; indicates the request for read from pertpherals. < Reg >

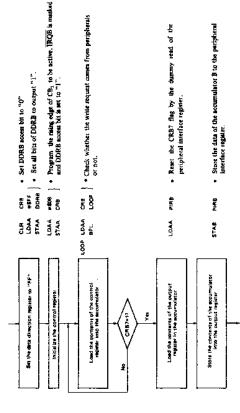

With operation using the interrupt injust is as follows. In this case, 3 port is used and farancer request is input to CB, and the IRQ flag is not at the riving of pr of CB.

HD6821, HD68A21, HD68B21

HD6821,HD68A21,HD68821

Interrupti request flag bits (CRA7, CRA6, CRB7 and CRB6) somether and they cannot be written on the prejibites and they cannot be about sets by write operation to the perjipitest interface register. So dummy read of operation in the prejibitest interface register is the read to incert the flags. To accept the next interrupt, it is essential to rest interrupt, that by dummy read of peripheral interface.

Experience of Section 1 and 1

• Hardwake Mode

The functions of CRA and CRB are similar bun not identical

The functions of CRA and CRB are similar bun not identical

to the hardwake modes, Post A is used for read hardwake

operation and Pot Bu used for work band-take mode,

CA, and CB, are used for interrupt input requests and CA,

and CB, are control output (samer) in hard-take mode,

Fig. 17 and Fig. 18 show the timing of hand-dake

Fig. 16, Fig. 17 and Fig. 18 show the timing of hand-dake

## <Read Hand-shake Mode> CRA5="!", CRA4="0" and CRA3="0"

A perspheral device puts the 8-bit data on the perspheral data lines affect the control output CA, goes "Low". The perspheral requests MPU to read the data by using CA, inport.

CRA7 flag is set and CA3, becomes "High" (CA3 auto-matically becomes "High" by the interrupt CA3, I'lls indicates the periphent to maintain the current data and not to transfer the next data.

MPU accepts the read request by IROA hardware interrupt or CRA read. Then MPU reads the peripheral register A. CA, goes "Low" on the following edge of read Emble publis. This informs that the peripheral can set the next data to post. A.

CWrite Hand-Schale > ("Red 2 = "Q")

(Red 2 = "") (Red 2 = "Q") and CRE3 = "Q"

A periphend device requests MPU to write the data by using

(C) proper CRE yourput remains "High" mail MPU write

data to the periphend batterface register.

(RED Ting to set and MPU ancepts the write request.

(SED) Ting to set and MPU ancepts the write request.

(SED) Ting to set and MPU ancepts the write request.

(SUM) Could be periphenal unterface register to reset CRE7

((showny zeals.)

(The mediat is outpoin to post Be through the output register.

(C) automatically becomes "Low" to tall the periphenal

three with also myor E.

In the periphenal data the data on Post B periphenal data lines

and set (E); to "Low" to tall MPU than the data on the

periphenal data lines has been taken and that each data can

be written to the periphenal interface register.

Aulie mode>

(RA5 = ")" (CRA1 = "0" and CRA3 = ")"

(RA5 = ")" (CRA4 = "0" and CRB3 = ")"

(RB4 = ")" (FRE4 = "0" and CRB3 = ")"

(FRE4 = ")" (FRE4 = "0" and FRE4 = 20.

88

**HITACHE**

330

18

1/0 32

#### **Getting Help**

If you have a technical question relating to the mechanical performance of your I/O 32 card that is not covered in the manual, please contact the dealer from whom you purchased the card. If you are experiencing difficulties with one particular program, contact the program's author or publisher.

In the event that the dealer or the publisher's support personnel cannot answer your question, call Applied Engineering Technical Support. The support representatives are experienced in the applications and uses of Applied Engineering products, but in order to provide a quick and effective answer to your question, they will need to know as much as possible about the hardware and software specifically related to your question. Please provide the technical support representative with the following information:

- ♦ The Applied Engineering product related to your question and its revision number.

- ♦ The original and current memory configuration of the card (if applicable).

- ♦ The model and revision of your computer.

- What peripherals are being used and what cards are in each slot.

- ♦ The name, version, and revision level of the software that you are experiencing problems with.

- ♦ The results of any test programs, diagnostics, or troubleshooting done by you, your dealer or your software publisher's support department.

Applied Engineering Technical Support (214) 241-6069

9 AM to 12:30 PM & 1:35 PM to 5 PM(CST)

Monday Through Friday

(Please call only the number above for technical support. Our sales office cannot transfer calls to the support lines.)

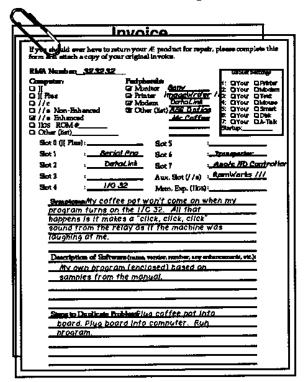

#### Returning a Product Include

If your product needs to be returned, the technical support representative will give you a Return Material Authorization (RMA) number.

- ☐ Record the RMA number for your own records.

- ☐ Write the RMA number on the outside of the package you send to us.

- ☐ Write the RMA number at the top of the return form included with your product package.

Fill out the Return Form on back of the yellow sheet marked, "Attention!" A correctly completed form will greatly reduce the time it takes to process and return your product.

Attach a copy of your original invoice to the return form.

❖ Warning: If you don't include an invoice products will be treated as out of warranty products and will be returned to you C.O.D. for the amount of the service charge.

A completed form should look something like the one below.

#### When You Ship

If you don't have the original packing material, wrap the board in anti-static material (preferrably the anti-static bag in which the card was originally shipped, however, aluminum foil will work fine). Pack it in a sturdy box cushioned with wadded papers (i.e. used computer paper or newspaper).

Warning: If your product is damaged due to inadequate packing, your warranty will be void.

Include the return form and invoice.

Send the package, shipping prepaid, to:

RMA#\_\_?\_\_ Applied Engineering Technical Support 3210 Belt Line Road, Suite 154 Dallas TX 75234

You should insure your package. Æ will not assume any responsibility for inadequate packing or loss or damage during shipping.

#### When We Receive

Our service department will use your completed form in an attempt to duplicate the problem.

If it is determined that your product is defective due to a manufacturing defect, your card will be repaired or replaced at Æ's option.

Any misuse, abuse, or non-Æ authorized alteration, modification and/or repair to the Applied Engineering product will void the warranty. This warranty will also be void if you use the Æ product for any purpose other than its intended use.

Your product will be fully tested before it is shipped back to you, transportation prepaid, via UPS regular delivery.

Once your product is received by Technical Support, it will be processed and delivered to our shipping department within 7 to 10 working days.

|   |  | _        |

|---|--|----------|

|   |  | <u> </u> |

|   |  |          |

|   |  |          |

|   |  | _        |

|   |  | _        |

| • |  | —        |

|   |  |          |

|   |  |          |

|   |  | J_       |

|   |  |          |

|   |  | _        |

|   |  | ~~       |

|   |  |          |

|   |  | _        |

|   |  | <u> </u> |

|   |  | _        |

|   |  | _        |

|   |  |          |

|   |  | ~        |

|   |  | -        |

|   |  |          |

|   |  | _        |

|   |  |          |